很多企業(yè)在產(chǎn)品開發(fā)時都會遇到同一個困惑:

為什么同一份原理圖,有的PCB一次打樣就能順利量產(chǎn)�����,而有的卻反復(fù)改版�����、周期延誤���、成本失控?

答案很簡單——

決定量產(chǎn)結(jié)果的關(guān)鍵���,不在生產(chǎn),而在設(shè)計��。

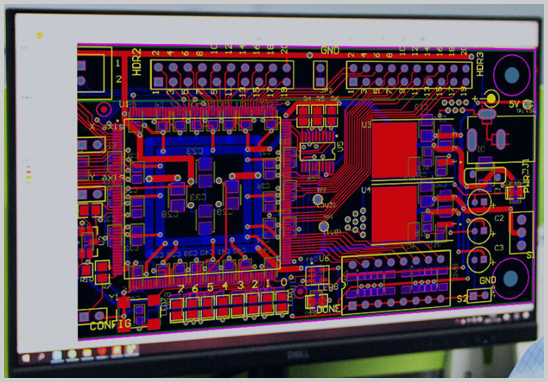

PCB設(shè)計并不是簡單的“畫線路板”��,而是一項融合電子���、電磁����、結(jié)構(gòu)、制造�、供應(yīng)鏈與測試工程的系統(tǒng)性工作。專業(yè)設(shè)計團(tuán)隊在正式布局前�����,都會先確認(rèn)以下5個關(guān)鍵決策點(diǎn)��。

一��、層疊結(jié)構(gòu)規(guī)劃:所有性能指標(biāo)的起點(diǎn)

層疊結(jié)構(gòu)(Stackup)決定了PCB的三項底層性能:

- 信號質(zhì)量

- 電磁兼容性

- 制造穩(wěn)定性

根據(jù)IPC發(fā)布的設(shè)計規(guī)范建議:

> 中高速或高密度電路必須在布局前完成層疊定義���。

設(shè)計階段應(yīng)明確:

- 板層數(shù)量

- 銅厚與介質(zhì)厚度

- 阻抗控制需求

- 盲孔/埋孔結(jié)構(gòu)

若等布局完成才確定層疊�,往往意味著整板必須重做���。

二��、可制造性設(shè)計(DFM):量產(chǎn)良率的決定因素

打樣能做出來����,并不代表量產(chǎn)能穩(wěn)定生產(chǎn)。

樣板階段通常可通過特殊工藝完成����,而量產(chǎn)必須滿足工藝窗口。

必須在設(shè)計階段驗(yàn)證:

- 最小線寬線距是否滿足量產(chǎn)能力

- 孔徑與板厚比是否合理

- 焊盤設(shè)計是否符合批量回流焊條件

- 阻焊橋是否穩(wěn)定

行業(yè)統(tǒng)計顯示:

超過60%的量產(chǎn)異常源于DFM缺失���,而非電路設(shè)計錯誤。

三���、信號完整性與電源完整性:高速板必須提前規(guī)劃

只要涉及以下任一接口���,就必須在布局前進(jìn)行SI/PI設(shè)計:

- DDR

- PCIe

- USB3.x

- 千兆網(wǎng)絡(luò)

- 高速ADC/DAC

依據(jù)IEEE高速電路設(shè)計研究結(jié)論:

> 高速信號問題90%由布局結(jié)構(gòu)導(dǎo)致��,而不是布線細(xì)節(jié)��。

關(guān)鍵規(guī)劃包括:

- 連續(xù)參考平面

- 差分阻抗控制

- 回流路徑設(shè)計

- 去耦電容拓?fù)洳季?/span>

這些問題如果后期才發(fā)現(xiàn)��,通常只能重新布局�。

四����、BOM與器件供應(yīng)策略:防止項目停產(chǎn)的核心措施

很多項目樣板測試通過�,卻無法進(jìn)入量產(chǎn)���,原因并不是PCB,而是元器件供應(yīng)失效����。

設(shè)計階段必須同步完成:

- 可替代料驗(yàn)證

- 生命周期評估

- 封裝兼容性設(shè)計

- 多供應(yīng)商策略

成熟硬件團(tuán)隊普遍要求:

> 關(guān)鍵器件必須至少兩家供應(yīng)來源。

否則一旦原廠停產(chǎn)�,整板產(chǎn)品將直接停產(chǎn)��。

五�、測試與可維護(hù)性設(shè)計:量產(chǎn)后的成本控制關(guān)鍵

很多產(chǎn)品上市后才發(fā)現(xiàn):

- 無法快速檢測故障

- 維修效率低

- 良率統(tǒng)計困難

這些問題幾乎全部源于設(shè)計階段沒有考慮DFT(可測試性設(shè)計)����。

必須預(yù)留設(shè)計內(nèi)容:

- ICT測試點(diǎn)

- 功能測試接口

- 調(diào)試通信口

- 電壓測量節(jié)點(diǎn)

工程實(shí)踐原則是:

不可測試節(jié)點(diǎn) = 不可驗(yàn)證質(zhì)量節(jié)點(diǎn)

為什么專業(yè)PCB設(shè)計服務(wù)更容易量產(chǎn)成功���?

因?yàn)閷I(yè)設(shè)計公司并不僅僅負(fù)責(zé)畫板�����,而是在設(shè)計階段就同步完成整套量產(chǎn)預(yù)評估�����,包括:

- 工藝可行性驗(yàn)證

- 成本結(jié)構(gòu)優(yōu)化

- 器件供應(yīng)風(fēng)險評估

- 批量良率預(yù)測

這相當(dāng)于在產(chǎn)品開發(fā)早期就做了一次“量產(chǎn)預(yù)演”���。

企業(yè)客戶最常問的3個PCB設(shè)計問題

1)什么時候開始做PCB設(shè)計最合適?

原理圖確認(rèn)后立即啟動�����。越晚介入����,改動成本越高。

2)多層板一定比雙層板好嗎���?

不是。層數(shù)增加意味著:

- 成本上升

- 壓合風(fēng)險增加

- 制造周期變長

只有布線密度或電氣性能需求才需要增加層數(shù)����。

3)BGA封裝設(shè)計為什么要求經(jīng)驗(yàn)��?

因?yàn)锽GA涉及:

- 逃線策略

- 焊盤結(jié)構(gòu)

- 阻抗控制

- 回流路徑

設(shè)計稍有偏差�����,就會導(dǎo)致焊接缺陷或信號異常。

總結(jié):真正決定量產(chǎn)成功的不是工廠���,而是設(shè)計階段

一塊PCB能否順利量產(chǎn)�,本質(zhì)取決于設(shè)計階段是否完成以下五項前置規(guī)劃:

1)層疊結(jié)構(gòu)定義

2)可制造性驗(yàn)證

3)信號與電源完整性規(guī)劃

4)器件供應(yīng)策略

5)測試接口設(shè)計

如果這些在設(shè)計階段已經(jīng)確認(rèn)��,后續(xù)生產(chǎn)通常只剩執(zhí)行問題����;

如果沒有提前規(guī)劃�,量產(chǎn)階段就會變成“試錯現(xiàn)場”��。

深圳宏力捷推薦服務(wù):PCB設(shè)計打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料